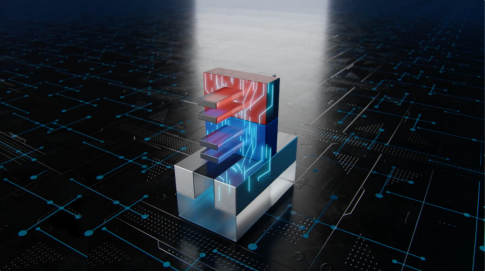

在IEDM 2023上,英特尔展示了结合背面供电和直接背面触点的3D堆叠CMOS晶体管,这些开创性的技术进展将继续推进摩尔定律。

2023年12月9日,英特尔在IEDM 2023(2023 IEEE 国际电子器件会议)上展示了多项技术突破,为其未来的制程路线图提供了丰富的创新技术储备,充分说明了摩尔定律仍在不断演进。具体而言,英特尔研究人员在大会上展示了结合背面供电和直接背面触点(direct backside contacts)的3D堆叠CMOS晶体管,分享了近期背面供电研发突破的扩展路径(如背面触点),并率先在同一块300毫米晶圆上,而非封装中,成功实现了硅晶体管与氮化镓(GaN)晶体管的大规模单片3D集成。

英特尔公司高级副总裁兼组件研究总经理Sanjay Natarajan表示:“我们正在进入制程技术的埃米时代,展望‘四年五个制程节点’计划实现后的未来,持续创新比以往任何时候都更加重要。在IEDM 2023上,英特尔展示了继续推进摩尔定律的研究进展,这显示了我们有能力面向下一代移动计算需求,开发实现晶体管进一步微缩和高能效比供电的前沿技术。”

晶体管微缩和背面供电是满足世界对更强大算力指数级增长需求的关键。一直以来,英特尔始终致力于满足算力需求,表明其技术创新将继续推动半导体行业发展,也仍然是摩尔定律的“基石”。英特尔组件研究团队不断拓展工程技术的边界,包括晶体管堆叠,背面供电技术的提升(有助于晶体管的进一步微缩和性能提升),以及将不同材料制成的晶体管集成在同一晶圆上。

英特尔近期在制程技术路线图上的诸多进展,包括PowerVia背面供电技术、用于先进封装的玻璃基板和Foveros Direct,彰显了英特尔正在通过技术创新不断微缩晶体管。这些创新技术均源自英特尔组件研究团队,预计将在2030年前投产。

在IEDM 2023上,英特尔组件研究团队同样展示了其在技术创新上的持续投入,以在实现性能提升的同时,在硅上集成更多晶体管。研究人员确定了所需的关键研发领域,旨在通过高效堆叠晶体管继续实现微缩。结合背面供电和背面触点,这些技术将意味着晶体管架构技术的重大进步。随着背面供电技术的完善和新型2D通道材料的采用,英特尔正致力于继续推进摩尔定律,在2030年前实现在单个封装内集成一万亿个晶体管。

英特尔实现了业界领先的、突破性的3D堆叠CMOS晶体管,结合了背面供电和背面触点技术:

•英特尔在IEDM 2023上展示了业界领先的最新晶体管研究成果,能够以微缩至60纳米的栅极间距垂直地堆叠互补场效应晶体管(CFET)。该技术可通过晶体管堆叠提升面积效率(area efficiency)和性能优势,还结合了背面供电和直接背面触点。该技术彰显了英特尔在GAA(全环绕栅极)晶体管领域的领先地位,展示了英特尔在RibbonFET之外的创新能力,从而能够领先竞争。

超越其“四年五个制程节点”计划,以背面供电技术继续微缩晶体管,英特尔确定了所需的关键研发领域:

• 英特尔的PowerVia将于2024年生产准备就绪,率先实现背面供电。英特尔组件研究团队在IEDM 2023上发表的研究明确了超越PowerVia,进一步拓展背面供电技术的路径,及所需的关键工艺进展。此外,该研究还强调了对背面触点和其它新型垂直互联技术的采用,从而以较高的面积效率堆叠器件。

英特尔率先在同一块300毫米晶圆上成功集成硅晶体管和氮化镓晶体管,且性能良好:

•在IEDM 2022上,英特尔聚焦于性能提升,以及为实现300毫米硅基氮化镓(GaN-on-silicon)晶圆开辟一条可行的路径。今年,英特尔在硅和氮化镓的工艺集成方面取得了进展,成功实现了一种高性能、大规模的集成电路供电解决方案,名为“DrGaN”。英特尔的研究人员率先在这一技术领域实现了良好的性能,有望让供电解决方案满足未来计算对功率密度和能效的需求。

英特尔推进2D晶体管领域的研发工作,以使其在未来继续按照摩尔定律的节奏微缩下去:

•过渡金属二硫属化物(TMD, Transition metal dichalcogenide)2D通道材料让晶体管物理栅极长度有机会微缩到10纳米以下。在IEDM 2023上,英特尔将展示高迁移率(high-mobility)的过渡金属二硫属化物晶体管原型,用于NMOS(n型金属氧化物半导体)和PMOS(p型金属氧化物半导体)这两大CMOS关键组件。此外,英特尔还将展示其率先实现的两项技术:GAA 2D过渡金属二硫属化物PMOS晶体管和在300毫米晶圆上制造的2D PMOS晶体管。